4到16译码器的工作原理是什么?

作者:佚名 来源:未知 时间:2025-02-17

4-16译码器是一种数字电路组件,广泛应用于各种电子设备中。其工作原理相对直观但功能强大,能够将4位二进制输入信号转换为16条唯一的输出线路中的一条高电平信号,而其他输出线路则保持低电平。这种转换机制在数字系统中非常重要,特别是在需要选择或激活多个设备中的一个时。

译码器的基本功能是解码,即将输入的二进制代码转换成对应的独热码(One-Hot Code)。在4-16译码器中,输入是一个4位的二进制数,范围从0000到1111,总共16种可能的组合。输出则是一个16位的线路,每一位对应一个可能的输入组合。当某个特定的4位二进制数输入时,对应的输出线路会被置为高电平(通常为5V或3.3V,取决于系统电压),而其他所有线路则保持低电平(0V)。

为了实现这一功能,译码器内部包含了一系列逻辑门电路。这些逻辑门通常是由与门(AND gates)和或门(OR gates)组合而成。输入的4位二进制数首先被送到一组与门中,每组与门对应于输出线路的一个可能状态。例如,当输入为0000时,只有与第一组与门相关联的线路会被激活,而其他所有与门都会因为至少有一个输入为低电平而输出低电平。

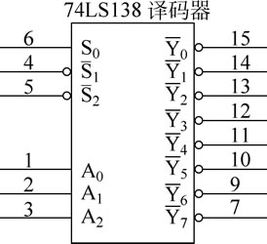

具体来说,每个与门都有4个输入端,分别连接到4位二进制数的每一位。此外,每个与门还有一个使能端(Enable),用于控制该与门是否参与逻辑运算。在译码器中,通常会有一个全局使能端,用于控制整个译码器是否工作。当全局使能端被激活时,译码器开始工作;当它被禁用时,所有输出都被强制为低电平,无论输入是什么。

为了产生独热码输出,译码器还需要使用或门。每个输出线路都连接到一个或门上,该或门接收来自所有与门中与该输出线路相对应的那些与门的输出。这样,当且仅当某个特定的4位二进制数输入时,对应的与门组会输出高电平,进而通过或门使对应的输出线路置为高电平。

除了基本的解码功能外,4-16译码器通常还具有一些附加功能,以增强其灵活性和实用性。例如,一些译码器具有一个低电平有效使能端(Active-Low Enable),当该端被置为低电平时,译码器开始工作。此外,一些译码器还具有一个或多个选通输出(Strobe Outputs),用于指示当前是否有有效的输出被选中。这些选通输出通常被用作其他数字电路的同步信号。

在实际应用中,4-16译码器广泛用于多路选择器、数据分配器以及存储器地址解码等场合。例如,在多路选择器中,译码器可以将输入的地址信号转换为选择信号,以从多个数据源中选择一个进行输出。在数据分配器中,译码器则用于将输入的控制信号转换为多个输出线路中的一个激活信号,以将数据发送到指定的目标设备。在存储器地址解码中,译码器将输入的存储器地址转换为对应的存储单元选择信号,以实现数据的读写操作。

值得注意的是,虽然4-16译码器在功能上是相当直观的,但在实际电路中,其实现可能需要考虑一些额外的因素。例如,为了提高电路的抗干扰能力,译码器的输入和输出通常都需要进行适当的缓冲和驱动处理。此外,为了避免因竞争条件导致的输出不稳定现象,译码器的内部逻辑设计也需要进行仔细的优化和调整。

此外,随着半导体技术的不断发展,现代的4-16译码器芯片已经变得越来越小巧、高效和可靠。这些芯片通常采用CMOS工艺制造,具有低功耗、高速度和长寿命等优点。同时,为了满足不同应用场合的需求,市场上也出现了各种类型和规格的译码器芯片,如具有三态输出的译码器、可编程译码器等。

在可编程译码器中,用户可以通过编程来改变译码器的输入-输出映射关系,从而使其适应不同的应用需求。这种灵活性极大地扩展了译码器的应用范围,使其在自动化控制系统、通信设备、计算机外设等领域中得到了广泛的应用。

总的来说,4-16译码器是一种非常重要的数字电路组件,其工作原理基于二进制数的解码和独热码的产生。通过合理的逻辑门电路设计,译码器能够将输入的4位二进制数转换为16条唯一的输出线路中的一条高电平信号。这种转换机制在数字系统中具有广泛的应用价值,特别是在需要选择或激活多个设备中的一个时。同时,随着半导体技术的不断进步和应用需求的不断变化,译码器也在不断发展和完善,以适应更加复杂和多样化的应用场景。